## INVESTING IN YOUR FUTURE

## Final results of the ERDF project No. 1.1.1/16/A/203 "Multilayer silicon nanocapacitor with improved dielectric layers"

After the midterm of the project (28 Feb 2018) and until the end of its implementation, the work focused on testing the repeatability of the manufacturing technology of a nanocapacitor with a multilayer  $Si_3N_4$  dielectric, as well as developing a prototype of the corresponding manufacturing technology in a laboratory environment. The implementation of the project was completed on February 29, 2020.

As a result of the project, a method for depositing a multilayer  $Si_3N_4$  dielectric for applications in nanocapacitors was developed. According to this method, several  $Si_3N_4$  nanolayers are deposited on top of each other using a chemical vapour deposition method in a chemical reaction between the gases silane (SiH<sub>4</sub>) and ammonia (NH<sub>3</sub>):  $3SiH_4 + 4NH_3 \rightarrow Si_3N_4 + 12H_2$ . After deposition of each nanolayer, the supply of SiH<sub>4</sub> gas to the deposition reactor is stopped and the surface of the deposited  $Si_3N_4$  is annealed at 700-800 °C in the NH<sub>3</sub> gas stream. After annealing, the SiH<sub>4</sub> gas supply is resumed again and the next  $Si_3N_4$  nanolayer is deposited. Deposition of the nanolayers and annealing of their surface in the NH<sub>3</sub> gas stream is repeated until the desired number of dielectric  $Si_3N_4$  nanolayers is reached.

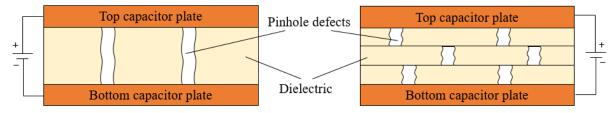

The developed method of dielectric deposition prevents the formation of pinhole defects in a thin dielectric layer. Pinholes are a typical type of defect in thin dielectric layers, the probability of which increases with a decrease in the thickness of the dielectric layer to several nanometers. Pinhole defects can cause an electrical short circuit between the top and bottom electrodes of the capacitor, and pinhole defects reduce the breakdown voltage of the capacitor. Pinhole defects can be prevented by fabricating a dielectric from several nanolayers of the same material superimposed on each other. In this case, each subsequent layer covers the pinhole defects of the previous layer, as shown schematically in Figure 1.

Fig. 1. Prevention of the pinhole defects in a multilayer dielectric: on the left – a singlelayered dielectric in which pinhole defects grow through the full thickness of the dielectric; on the right – a multilayer dielectric in which each subsequent dielectric nanolayer covers the pinholes of the previous nanolayer.

On December 23, 2019, we submitted *a patent application* No. P-19-17 " Deposition method of a thin multilayer dielectric" to the Latvian Patent Office (LPO). Publication A of the patent application (LV15492A) was published in the Official Gazette of LPO on March 20, 2020 (page 305): <u>https://www.lrpv.gov.lv/sites/default/files/20200320.pdf#page=305</u>

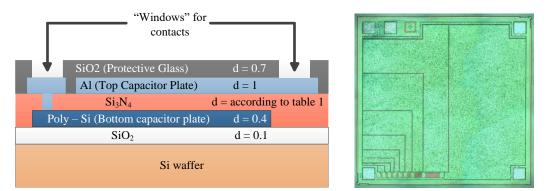

Based on the developed method of multilayer  $Si_3N_4$  dielectric deposition, the project resulted in the development of two prototypes of the nanocapacitor fabrication technology. The thickness of the multi-layered  $Si_3N_4$  dielectric in the developed prototypes was 40 and 60 nm (Table 1). *The first prototype* (Figure 2) is a nanocapacitor with the bottom electrode made from polycrystalline silicon (Poly-Si). Polycrystalline silicon is a typical material used for manufacturing electrodes in microelectronic components. The mid-term results of the project showed that the Poly-Si electrode has a grainy structure and its surface roughness is comparable to the thickness of the  $Si_3N_4$  nanolayer when the  $Si_3N_4$  nanolayer is a few tens of nanometers thick<sup>1</sup>. In this case, the roughness of the  $Si_3N_4$  nanolayer replicates the roughness of Poly-Si. Increased roughness of the dielectric is undesirable in the case of a nanocapacitor because this increases the leakage current and the probability of dielectric breakdown.

Fig. 2. Prototype 1 is a nanocapacitor that has a bottom electrode made from Poly-Si. The structure of the layers is shown on the left-hand side. The capacitor topology is shown on the right-hand side. The area of one capacitor area is 2.95 mm<sup>2</sup>, *d* is the thickness of the layers (in μm). The parameters of the Si<sub>3</sub>N<sub>4</sub> dielectric are shown in Table 1.

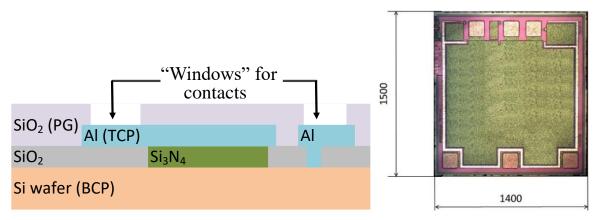

To eliminate the drawback of the Poly-Si electrode, we developed *the second prototype* of the nanocapacitor fabrication technology (Figure 3). This prototype uses a low-resistivity Si wafer as a bottom electrode of the nanocapacitor. The roughness of the Si wafer is only about 0.1 nm, which does not influence the roughness of  $Si_3N_4$  nanolayer deposited on the top of it<sup>1</sup>.

Table 1

Parameters of the multi-layered Si<sub>3</sub>N<sub>4</sub> dielectric – thickness and number of nanolayers

| Thickness ( $d$ ) of the multi-<br>layered Si <sub>3</sub> N <sub>4</sub> dielectric, nm | Number of Si <sub>3</sub> N <sub>4</sub><br>nanolayers in the<br>dielectric |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 40                                                                                       | 5                                                                           |

| 60                                                                                       | 5                                                                           |

<sup>&</sup>lt;sup>1</sup> Avotina, L., Pajuste, E., Romanova, M., Enichek, G., Zaslavskis, A., Kinerte, V., Avotins, J., Dekhtyar, Yu., Kizane, G. Surface morphology of single and multilayer silicon nitride dielectric nano-coatings. *Materials Science (Medžiagotyra)*, 2020, 26(1), pp.25-29. <u>http://matsc.ktu.lt/index.php/MatSc/article/view/21479</u>

Fig. 3. Prototype 2 is a nanocapacitor with a multi-layered Si<sub>3</sub>N<sub>4</sub> dielectric where a lowresistance Si wafer is used as a bottom electrode. The structure of the layers is shown on the left-hand side, the capacitor topology is shown on the right-hand side. The area of one capacitor is 2.1 mm<sup>2</sup>. The parameters of the Si<sub>3</sub>N<sub>4</sub> dielectric are shown in Table 1.

Table 2 compares the parameters of the developed prototypes with publicly available data about their modern analogues (*state-of-the-art*).

Table 2

Comparison between the developed technology prototypes and the latest publicly available analogues (*state-of-the-art*)

| Parameter                                                                        |                                              |           | Prototype 1 (uses Poly-<br>Si electrode)                       |                       | Prototype 2 (uses low-<br>resistance Si wafer) |                       |  |

|----------------------------------------------------------------------------------|----------------------------------------------|-----------|----------------------------------------------------------------|-----------------------|------------------------------------------------|-----------------------|--|

|                                                                                  |                                              |           | The thickness of Si <sub>3</sub> N <sub>4</sub> multilayer, nm |                       |                                                |                       |  |

|                                                                                  |                                              |           | 40                                                             | 60                    | 40                                             | 60                    |  |

| Dielectric strength of                                                           | of Developed in the                          |           | $0.45 * 10^{1}$                                                | $0.47 * 10^{1}$       | $0.50 * 10^{1}$                                | $0.45 * 10^{1}$       |  |

| the nanocapacitor                                                                | project                                      |           |                                                                |                       |                                                |                       |  |

| dielectric layer <sup>2</sup> ,                                                  | The modern level of                          |           | 1*10                                                           |                       |                                                |                       |  |

| MV/cm                                                                            | development <sup>3, 4</sup>                  |           | $1*10^{1}$                                                     |                       |                                                |                       |  |

| C, pF/mm <sup>2</sup>                                                            | Developed                                    | at 10 kHz | 1700                                                           | 1300                  | 2200                                           | 2200                  |  |

|                                                                                  | in the project                               | at 1 MHz  | 1700                                                           | 1300                  | 2200                                           | 2200                  |  |

|                                                                                  | The modern level of development <sup>5</sup> |           | 480                                                            |                       |                                                |                       |  |

| Density of leakage current $I_{LEAK}$ in DC mode <sup>6</sup> , A/m <sup>2</sup> | Developed in the                             |           | <1,7*10-5                                                      | <1,7*10 <sup>-5</sup> | <1,7*10 <sup>-5</sup>                          | <1,7*10 <sup>-5</sup> |  |

|                                                                                  | project                                      |           |                                                                |                       |                                                |                       |  |

|                                                                                  | The modern level of                          |           | 5*10 <sup>-2</sup>                                             | $1*10^{-3}$           | 5*10 <sup>-2</sup>                             | $1*10^{-3}$           |  |

|                                                                                  | development <sup>5</sup>                     |           |                                                                |                       |                                                |                       |  |

<sup>&</sup>lt;sup>2</sup> The ratio: (Breakdown voltage)/ (thickness of the multi-layered Si<sub>3</sub>N<sub>4</sub> dielectric).

<sup>&</sup>lt;sup>3</sup> https://en.wikipedia.org/wiki/Silicon\_nitride, viewed 26.02.2020.

<sup>&</sup>lt;sup>4</sup> Yota, J. (2011). Effects of deposition method of PECVD silicon nitride as MIM capacitor dielectric for GaAs HBT technology. *ECS Transactions*, *35*(4), 229

<sup>&</sup>lt;sup>5</sup> S. T. Patton, A. J. Frasca, J. W. Talnagi, D. J. Hyman, B.S. Phillips, J.G. Jones, R. A. Vaia, A. A. Voevodin. (2013). Effect of space radiation on the leakage current of MEMS insulators. *IEEE transactions on nuclear science*, 60(4), 3074-3083.

$<sup>^{6}</sup>$  An operating voltage of 5 V and 10 V, respectively, was used to determine the parameter for 40 nm and 60 nm thick dielectric.

| Parameter                                     |                                              | Prototype 1 (uses Poly-<br>Si electrode)                       |           | Prototype 2 (uses low-<br>resistance Si wafer) |           |  |  |  |

|-----------------------------------------------|----------------------------------------------|----------------------------------------------------------------|-----------|------------------------------------------------|-----------|--|--|--|

|                                               |                                              | The thickness of Si <sub>3</sub> N <sub>4</sub> multilayer, nm |           |                                                |           |  |  |  |

|                                               |                                              | 40                                                             | 60        | 40                                             | 60        |  |  |  |

| Resistance to ionizing radiation              |                                              |                                                                |           |                                                |           |  |  |  |

| Leakage current in DC mode, I <sub>LEAK</sub> | Developed in the project                     | No impact                                                      | No impact | No impact                                      | No impact |  |  |  |

|                                               | The modern level of development <sup>5</sup> | No impact                                                      | No impact | No impact                                      | No impact |  |  |  |

The cells highlighted in yellow show parameters that are significantly superior to their modern counterparts. The parameters highlighted in grey are at the same level as their modern counterparts. In general, the comparison shows that the parameters of nanocapacitors developed in the project exceed or are at the same level as their modern counterparts.

## Dissemination of the project results in scientific publications and at conferences

Five scientific articles were published in journals or conference proceedings indexed by the SCOPUS database:

- M. Romanova, L. Avotina, M. Andrulevicius, Yu. Dekhtyar, G. Enichek, G. Kizane, M. Novotný, E. Pajuste, P. Pokorný, T. Yager, A. Zaslavski. Radiation resistance of nanolayered silicon nitride capacitors. *Nuclear Instruments and Methods in Physics Research Section B: Beam Interactions with Materials and Atoms*, 2020, 471, pp.17-23. <u>https://doi.org/10.1016/j.nimb.2020.03.010</u>

- Dekhtyar, Yu., Enichek, G., Romanova, M., Schmidt, B., Vilken, A., Yager, T., Zaslavski, A. Charge Trap Analysis of nanolayer Si<sub>3</sub>N<sub>4</sub> and SiO<sub>2</sub> by electron irradiation assisted photoelectron emission. *Physica B: Physics of Condensed Matter*, 2020, 586, 412123.

https://doi.org/10.1016/j.physb.2020.412123

- Avotina, L., Pajuste, E., Romanova, M., Enichek, G., Zaslavskis, A., Kinerte, V., Avotins, J., Dekhtyar, Yu., Kizane, G. Surface morphology of single and multilayer silicon nitride dielectric nano-coatings. *Materials Science (Medžiagotyra)*, 2020, 26(1), pp.25-29. <u>http://matsc.ktu.lt/index.php/MatSc/article/view/21479</u>

- Dekhtyar, Yu., Avotiņa, L., Enichek, G., Romanova, M., Schmidt, B., Shulzinger, E., Sorokins, H., Vilken, A., Zaslavskis, A. Interface of Silicon Nitride Nanolayers with Oxygen Deficiency. 2018 16th Biennial Baltic Electronics Conference, Estonia, Tallinn, 8-10 October, 2018. Tallinn University of Technology: 2018, pp.1-4. https://ieeexplore.ieee.org/document/8600964

- Avotiņa, L., Pajuste, E., Romanova, M., Zaslavskis, A., Enichek, G., Kinerte, V., Zariņš, A., Lescinskis, B., Dekhtyar, Yu., Kizane, G. FTIR Analysis of Electron Irradiated Single and Multilayer Si<sub>3</sub>N<sub>4</sub> Coatings. *Key Engineering Materials*, 2018, 788, pp.96-101. www.scientific.net/KEM.788.96

The results of the project were discussed at international scientific conferences:

- *A)* <u>Presentations at conferences with publications in conference proceedings or abstract</u> <u>book:</u>

- 1. Avotina, L., Dekhtyar, Yu., Jenichek, G., Kizane, G., Pajuste, E., Romanova, M., Yager, T., Zaslavskis, A. Radiation stability of multilayer silicon nitride nanocapacitors. 20th International Conference on Radiation Effects in Insulators: Book of Abstracts, Kazakhstan, Nur-Sultan, 19-23 August 2019.

- Avotina, L., Romanova, M., Pajuste, E., Enichek, G., Zaslavskis, A., Dekhtyar, Yu., Kizane, G. Electrical properties of single and multilayer silicon nitride dielectric for applications in nanocapacitors. 21st International Conference-School "Advanced Materials and Technologies 2019": Book of Abstracts, Lithuania, Palanga, 19-23 August 2019.

- Andrulevičius, M., Avotiņa, L., Dekhtyar, Yu., Enichek, G., Romanova, M., Shulzinger, E., Sorokins, H., Tamulevičius, S., Vilken, A., Zaslavski, A. XPS, FTIR and photoelectron emission spectroscopies to analyze nanocapacitor silicon nitride nanolayered structures. 2nd International Conference on Nanomaterials Science and Mechanical Engineering: Book of Abstracts, Portugal, Aveiro, 9-12 July 2019.

- Yu. Dekhtyar, L. Avotiņa, G. Enichek, M. Romanova, B. Schmidt, E. Shulzinger, H. Sorokins, A. Viļķens, A. Zaslavskis. Interface of Silicon Nitride Nanolayers with Oxygen Deficiency. 2018 16<sup>th</sup> Biennial Baltic Electronics Conference, Estonia, Tallinn, 8-10 October 2018. <u>https://ieeexplore.ieee.org/document/8600964</u>

- L. Avotina, E. Pajuste, M. Romanova, A. Zaslavskis, G. Enichek, V. Kinerte, Yu. Dekhtyar, G. Kizane. Modifications of Silicon Nitride Bonds under Action of Accelerated Electrons. *RACIRI 2018 Summer School*, Germany, Rügen, 25 Aug-1 Sep. 2018.

- E. Pajuste, M. Romanova, L. Avotina, G. Enichek, A. Zaslavskis, V. Kinerte, Yu. Dekhtyar, G. Kizane. Surface Morphology of Single and Multilayered Silicon Nitride Dielectric Nanocoatings. 20<sup>th</sup> International Conference-School "Advanced Materials and Technologies", Lithuania, Palanga, 27-31 August 2018

- L. Avotina, E. Pajuste, M. Romanova, A. Zaslavskis, V. Kinerte, B. Lescinskis, Yu. Dekhtyar, G. Kizane. FT-IR Analysis of Electron Irradiated Single and Multilayer Si3N4 Coatings. 8<sup>th</sup> International Conference on Silicate Materials "BaltSilica 2018", Latvia, Riga, 30 May-1 Jun. 2018. <u>https://www.scientific.net/KEM.788.96</u>

- L. Avotina, Yu. Dekhtyar, M. Romanova, E. Shulzinger, B. Schmidt, A. Viļķens, A. Zaslavski, G. Enichek. Silicon Nitride Multi Nanolayer System Fabricated in One Reactor. 6<sup>th</sup> International Conference "Telecommunications, Electronics and Informatics (ICTEI 2018)", Moldova, Chisinau, 24-27 May 2018.

- M. Romanova, L. Avotiņa, R. Zariņš, A. Zariņš, J. Bitenieks, A. Vilimans, A. Zaslavskis, G. Kizane, Yu. Dekhtyar. Electrical properties of single-layer and multilayer Si<sub>3</sub>N<sub>4</sub> dielectric on Si substrate. 3<sup>rd</sup> International Conference "Innovative Materials, Structures and Technologies" (IMST2017), 27-29 September 2017, Riga, Latvia.

- L. Avotina, R. Zarins, E. Pajuste, M. Romanova, J. Bitenieks, J. Zicāns, A. Zaslavskis, Yu. Dekhtyar, G. Kizane. Influence of ionizing radiation on the Si<sub>3</sub>N<sub>4</sub> coatings on Si substrate. 19<sup>th</sup> International Conference-School "Advanced Materials and Technologies 2017", 27-31 August 2017, Palanga, Lithuania.

- 11. L. Avotina, R. Zarins, M. Romanova, E. Pajuste, A. Zaslavskis, Yu. Dekhtyar, G. Kizane. Characterisation of silicon nitride coatings irradiated with accelerated electrons and bremsstrahlung radiation. *International Conference "Functional Materials and Nanotechnologies 2017" (FMNT-2017)*, 24-27 April 2017, Tartu, Estonia.

- *B)* <u>Oral presentations at conferences without publication:</u>

- 12. L. Avotiņa, E. Pajuste, M. Romanova, A. Zaslavskis, Yu. Dekhtyar, G. Kizane. FTIR studies of radiation stability of multilayered silicon nitride thin films for nanocapacitors. 78<sup>th</sup> International Scientific Conference of the University of Latvia, Riga, Latvia, February 21, 2020.

- 13. T. Yager, A. Viļķens, E. Shulzinger, Yu. Dekhtyar, G. Jeņičeks, A. Zaslavskis. Investigation of electrical defects of dielectric layers of Si<sub>3</sub>N<sub>4</sub>. 60<sup>th</sup> International Scientific Conference of Riga Technical University, Riga, Latvia, October 17, 2019.

- 14. E. Pajuste, M. Romanova, L. Avotina, A. Zaslavskis, G. Enichek, G. Kizane, Yu. Dekhtyar. Influence of fabrication parameters on morphology of Si<sub>3</sub>N<sub>4</sub> dielectric of nanocapacitor. 77<sup>th</sup> International Scientific Conference of the University of Latvia, Riga, Latvia, February 1, 2019.

- 15. T. Yager, M. Romanova, Yu. Dekhtyar, A. Zaslavskis, G. Enichek, G. Kizane. Influence of manufacturing technology and ionizing radiation on electron emission properties of Si<sub>3</sub>N<sub>4</sub> dielectric nanolayers. 59<sup>th</sup> International Scientific Conference of Riga Technical University, October 11, 2018, Riga, Latvia

- 16. L. Avotiņa, E. Pajuste, M. Romanova, A. Zaslavskis, J. Dehtjars, G. Kizane. Characterization of chemical bonds in nanolayers of silicon nitride with FT-IR. 76<sup>th</sup> International Scientific Conference of the University of Latvia, Riga, Latvia, February 2, 2018.

- 17. M. Romanova, Yu. Dekhtyar, A. Vilimans, A. Zaslavskis, G. Kizane. Study of electrical defects in Si<sub>3</sub>N<sub>4</sub> dielectric layer. *58<sup>th</sup> International Scientific Conference of Riga Technical University*, October 13, 2017, Riga, Latvia.

## **Project photo-galleries online**

The seminar "Nanocapacitors in Latvia" organized for business companies on February 21, 2020: https://www.facebook.com/biedribaLETERA/posts/204933940884315

https://www.letera.lv/letera-biedri-iepazistas-ar-inovativu-nanokondensatoru-razosanastehnologiju

- The photo-gallery "We aim for the global nanocapacitor market!": <u>https://www.facebook.com/pg/rigastehniskauniversitate/photos/?tab=album&album\_id=3</u> <u>643198279053551</u>

- Information for media on a website of Riga Technical University: <u>https://www.rtu.lv/lv/universitate/masu-medijiem/zinas/atvert/rada-tehnologiju-kas-var-palidzet-latvijas-uznemumiem-ieklut-pasaules-nanokondensatoru-tirgu</u>

Published on March 13, 2020.